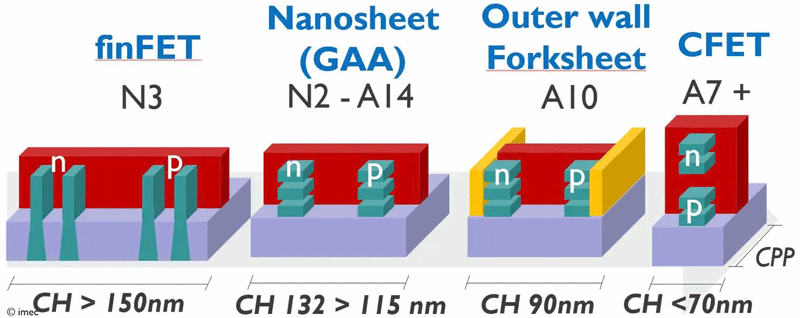

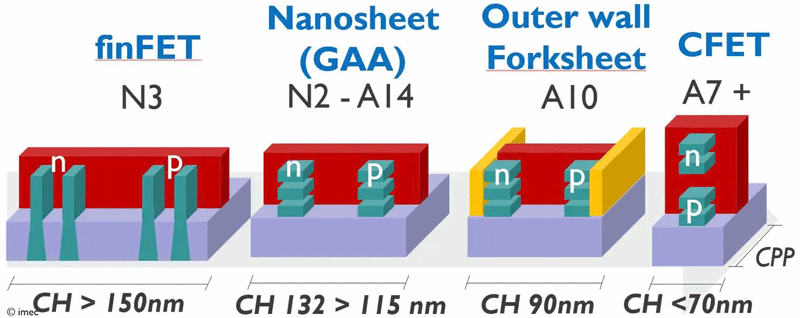

Около шести лет назад бельгийский центр Imec представил совершенно новую архитектуру транзисторов — CFET (комплементарные FET). Она должна была помочь с производством транзисторов с нормами производства менее 2 нм. Особенностью архитектуры стали раздельные наностраничные каналы (forksheet). Но технология оказалась сложна для производства, поэтому в Imec создали видоизменённый промежуточный вариант будущей архитектуры, представленный на днях.

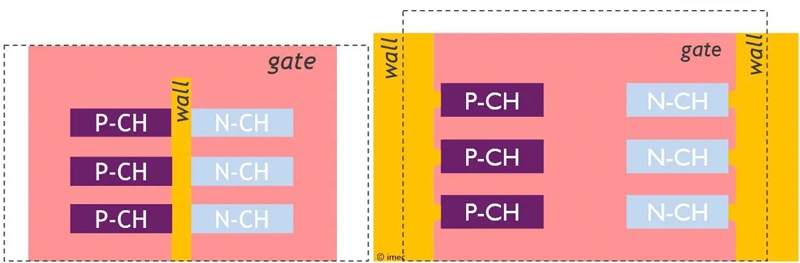

Суть архитектуры forksheet заключается в разделении диэлектрической перегородкой транзисторов n- и p-типа с общим круговым затвором (GAA). Перегородка или стена призвана минимизировать влияние соседних транзисторов друг на друга. В таком случае пару транзисторов с разной проводимостью можно изготовить на меньшей площади чипа, что, в итоге, приведёт к существенному снижению площади кристалла — до 20 %. Более того, Imec предложил располагать транзисторы друг над другом для реализации архитектуры CFET, что ещё сильнее уменьшило бы площадь чипов. Однако последующая работа над транзисторами с раздельными страницами показала, что идея с диэлектрической перегородкой крайне сложна при воплощении в производство.

Тончайшую перегородку из диэлектрика толщиной от 8 до 10 нм необходимо было изготавливать первой ещё до всех манипуляций с кристаллом и травлением транзисторов. Такие «издевательства» над собой выдержит далеко не каждый материал, что вело бы к высокому уровню брака. Тогда в Imec придумали гениальное решение — перегородки должны быть внешними. Они уже не отдаляли разнополярные транзисторы друг от друга, но они как бы изолировали пары транзисторов от соседних пар. Фактически это была изоляция транзисторов с одинаковой проводимостью.

При таком техпроцессе перегородки изготавливались одними из последних на кристалле. Такое решение позволяло использовать известные материалы. За счёт более толстых стен могла незначительно пострадать площадь размещения пар транзисторов, но зато все остальные выгоды в виде увеличения скорости работы (токов) и снижения утечек сохранялись. Более тонкий переход между наностраницами и внешней стенкой позволял затвору охватывать увеличенную площадь ребра каждого наностраничного канала, что существенно улучшало контроль над токами в транзисторных каналах.

Наконец, финальное изготовление внешних стенок вокруг транзисторных каналов повышало механическую напряжённость в наностраницах (в каналах транзисторов). Термин «напряжённый кремний» знаком всем, кто как минимум четверть века в теме производства чипов. В таких условиях повышается проводимость электронов и дырок в полупроводнике, что ведёт к повышению общей производительности чипов.

Разработчики признают, что за счёт повышения толщины внешних изолирующих перегородок forksheet-транзисторов до 15 нм общая площадь чипа может оказаться несколько больше, чем в случае использования внутренних перегородок, но это небольшая и вынужденная жертва. Моделирование в CAD ячеек SRAM и генераторов с использованием транзисторов с раздельными наностраницами и внешними перегородками показало, что в ячейках статической памяти новая схема для техпроцесса A10 (10 ангстрем) позволила сократить площадь на 22 % по сравнению с нанолистами A14 без изоляции за счёт более плотной упаковки однотипных устройств и уменьшения шага затворов.

Для схемы генератора под полной нагрузкой новая компоновка соответствует или превосходит производительность генераторов для техпроцессов A14 и 2 нм. Без нагрузки ток питания снижается примерно на 33 % (снижение утечек).

Опыт производства транзисторов с раздельными наностраницами будет иметь большое значение для разработки CFET, поскольку многие этапы процесса, материалы и концепции проектирования будут пересекаться. В forksheet-транзисторах устройства p-типа и n-типа располагаются рядом друг с другом. В отличие от них, в CFET нового поколения два разных типа транзисторов будут располагаться вертикально, хотя базовые технологии останутся прежними. Но это история середины 30-х годов, к которой мы ещё не раз вернёмся в будущем.