Обозреватель HardwareLuxx Андреас Шиллинг (Andreas Schilling) опубликовал изображения чиплетов настольных процессоров Intel Arrow Lake-S с пояснениями, демонстрирующими внутреннюю компоновку вычислительного блока с ядрами этих процессоров, а также вспомогательных чиплетов.

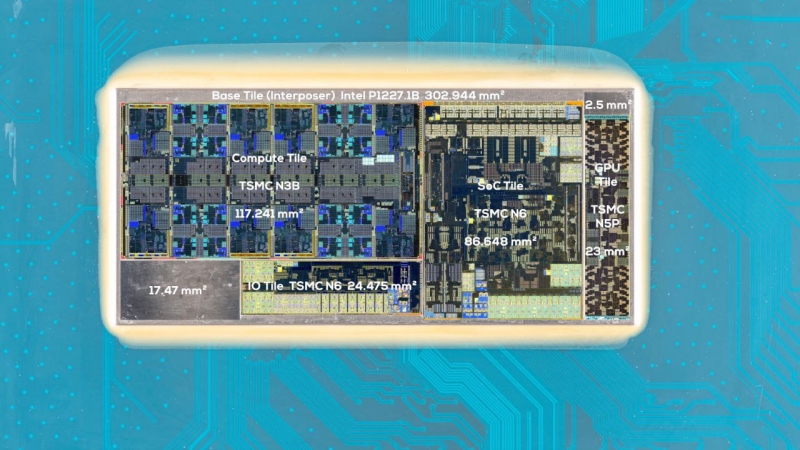

На первом изображении показан весь кристалл настольных процессоров Core Ultra 200S с большим вычислительным чиплетом в верхнем левом углу, чиплетом интерфейсов ввода-вывода (I/O Die) внизу, а также чиплетами SoC и встроенной графики (iGPU) справа. В нижнем левом углу и верхнем правом расположены чиплеты-пустышки, обеспечивающие структурную целостность кристалла процессора.

Чиплет с вычислительными ядрами производится на базе технологического процесса N3B (3 нм) компании TSMC и имеет площадь 117,241 мм². Блоки SoC и I/O Die изготавливаются по более зрелому техпроцессу TSMC N6 (6 нм). Площадь чиплета I/O Die составляет 24,475 мм², а SoC — 86,648 мм². Все чиплеты (или плитки, как их называет Intel) размещаются на подложке, выполненной по 22-нм техпроцессу Intel FinFET. Arrow Lake — первые процессоры Intel, в которых используются производственные технологии конкурента, за исключением базовой подложки.

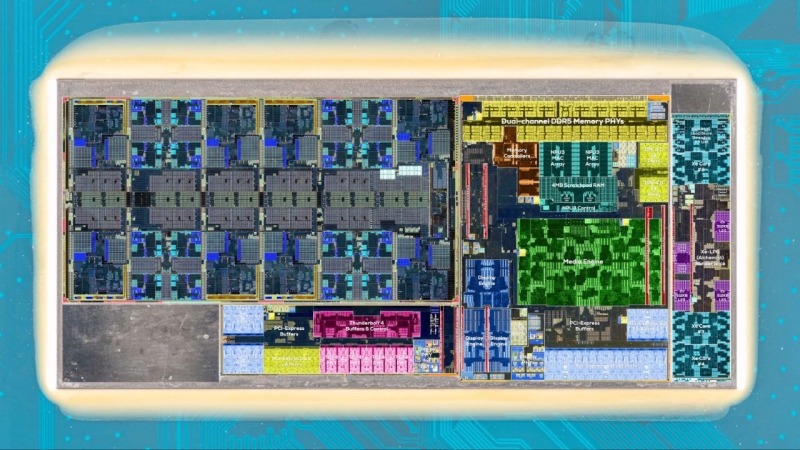

Следующее изображение выделяет все дополнительные компоненты вторичных чиплетов Arrow Lake. В составе I/O Die находятся контроллеры Thunderbolt 4 и схемы PHY дисплея, буферы PCI Express и TBT4 PHY и т. д. В составе SoC размещены контроллеры дисплея (Display Engine), медиа-движок, дополнительные схемы PCIe PHY, буферы и контроллеры памяти DDR5. Чиплет iGPU, изготовленный по техпроцессу TSMC N5P (5 нм), содержит четыре ядра Xe и блок рендеринга на базе Xe LPG (Arc Alchemist).

На последнем изображении в деталях показан чиплет с вычислительными ядрами процессоров Arrow Lake-S, отличающийся от других процессоров Intel с гибридной архитектурой больших и малых ядер. В Arrow Lake компания решила разместить энергоэффективные E-ядра между производительными P-ядрами, а не в отдельном кластере. Четыре из восьми P-ядер Lion Cove расположены по краям чиплета, четыре других — в центре кристалла. Четыре кластера E-ядер Skymont (по четыре ядра в каждом) размещены между «внешними» и «внутренними» P-ядрами. Такая конфигурация призвана снизить тепловую нагрузку при высокой загрузке P-ядер (например, во время игр).

Изображения также демонстрируют схему кэш-памяти процессоров Arrow Lake-S. На каждое P-ядро приходится по 3 МБ кэша L3 (всего 36 МБ), а на каждый кластер E-ядер — по 2 МБ кэша L2. Также оба типа ядер имеют общий кэш объёмом 1,5 МБ. Каждый кластер E-ядер находится всего в одном шаге от кольцевой шины и от P-ядра. Сама кольцевая шина, а также 36 МБ кэш-памяти L3, совместно используемой P- и E-ядрами (одно из ключевых нововведений Arrow Lake), расположены в центральной области чиплета.

Arrow Lake — одна из самых сложных процессорных архитектур Intel на сегодняшний день и первая чиплетная архитектура компании, выпущенная на рынок настольных ПК. Однако первый блин оказался комом: процессоры Arrow Lake-S разочаровали своей производительностью из-за проблем с задержками в шине, которая отвечает за соединение всех чиплетов. Intel пытается устранить эту проблему с помощью обновлений прошивки. Тем не менее в текущем виде настольные Core Ultra 200S не могут конкурировать с процессорами AMD Ryzen 9000 (особенно с Ryzen 7 9800X3D) и даже уступают по производительности в играх своим предшественникам (в частности, Core i9-14900K).